- 1. Описать функцию мультиплексора. Привести условное обозначение, таблицу истинности и логическую схему одноразрядного мультиплексора «4-в-1», описать «внутреннее» функционирование схемы.

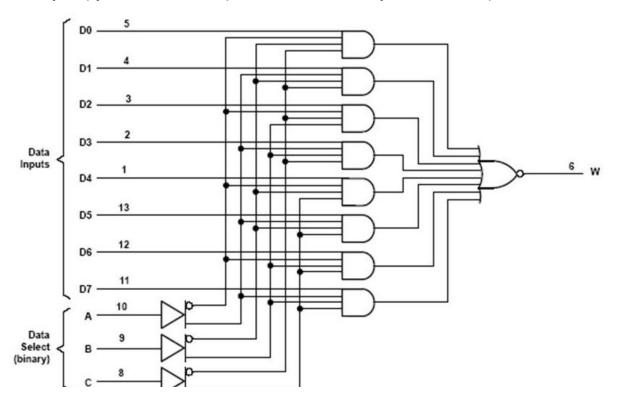

- 2. Описать функцию мультиплексора. Описать способ реализации произвольной логической функции при помощи мультиплексора. Привести схему, реализующую указанную ниже логическую функцию и описать ее работу: 5

- 3. Описать функцию мультиплексора. Привести и описать функционирование схемы мультиплексора «4-в-1», построенной на нескольких мультиплексорах «2-в-1».

6

7

- 4. Описать функцию демультиплексора. Привести условное обозначение, таблицу истинности и логическую схему одноразрядного демультиплексора «1-в-4», описать «внутреннее» функционирование схемы.

- 5. Описать функцию двоичного дешифратора. Привести условное обозначение, таблицу истинности и логическую схему двоичного дешифратора 2-х разрядного двоичного кода. Описать «внутреннее» функционирование схемы.

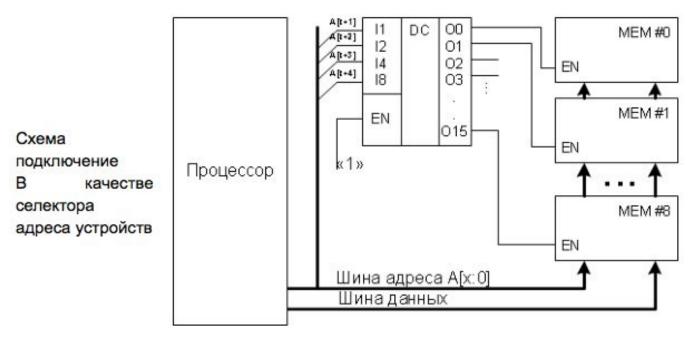

- 6. Описать функцию двоичного дешифратора. Привести схему подключения дешифратора «2-в-4» в качестве селектора адреса для 4-х устройств памяти, подключенных к общей шине (данных) ЭВМ, и описать функционирование этой схемы.

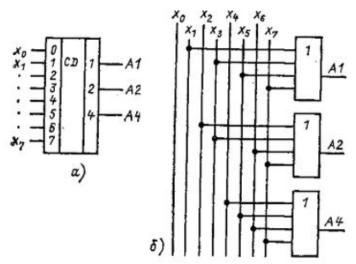

- 7. Описать функцию двоичного дешифратора. Описать способ реализации произвольной логической функции с использованием дешифратора и логического элемента ИЛИ. Привести схему, реализующую приведенную ниже логическую функцию и описать ее работу: Y=(! x 1· x 2· x 3·! x 4) + ( x 1·! x 2· x 3· x 4) + ( x 1· x 2· x 3·! x 4)

- 8. Описать функцию двоичного дешифратора. Привести и описать функционирование схемы наращивания размерности дешифратора: из нескольких двоичных дешифраторов «2-в-4» построить двоичный дешифратор «4-в-16».

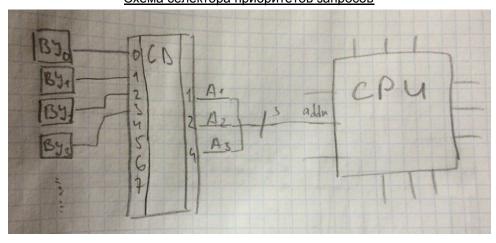

- 9. Описать функцию двоичного бесприоритетного шифратора и двоичного приоритетного шифратора. Привести условное обозначение двоичного шифратора «4-в-2». Привести таблицу истинности двоичного приоритетного шифратора «4-в-2». Привести схему селектора приоритетов запросов прерываний на базе приоритетного двоичного шифратора.

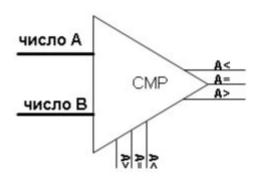

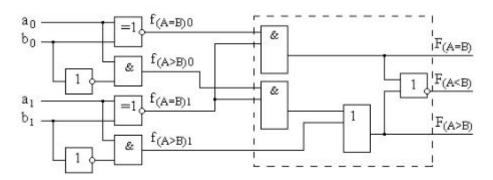

- 10. Привести условное обозначение, таблицу истинности и логическую схему полного компаратора по величине («больше-меньше-равно») для 2-х разрядных двоичных чисел. Описать «внутреннее» функционирование схемы.

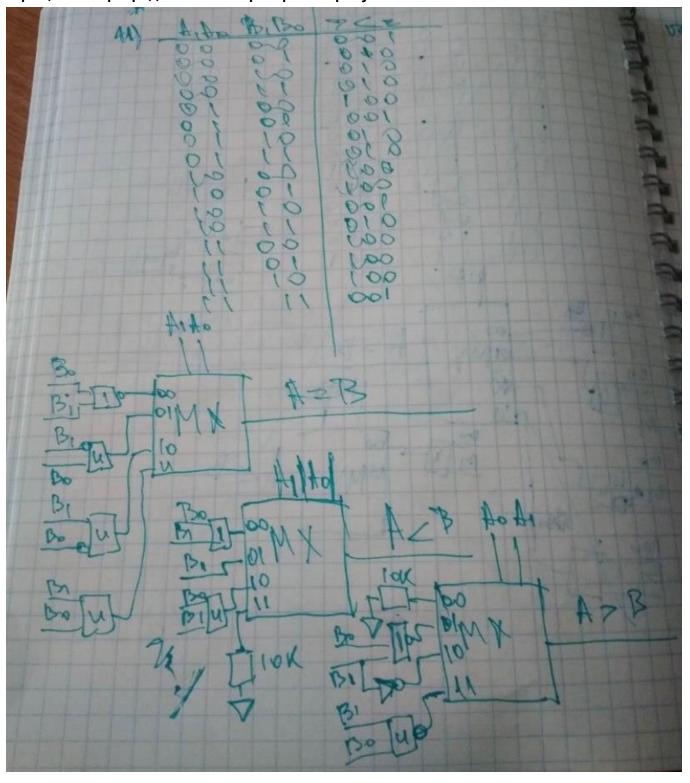

- 11. Привести схему полного компаратора по величине («больше-меньше-равно») для двух 2-х разрядных двоичных чисел, построенную на базе мультиплексора (-ов). Реализация входов наращивания разрядности компаратора НЕ требуется. 14

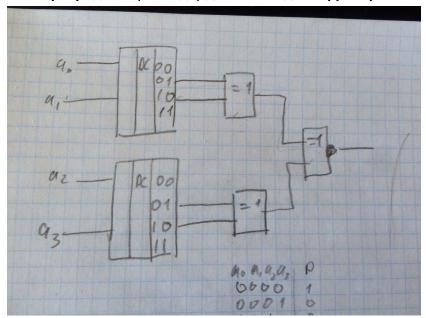

- 12. Привести схему вычисления бита чётности для 4-х разрядного двоичного слова, построенную на базе 2-х разрядных (2 входа) двоичных дешифраторов.15

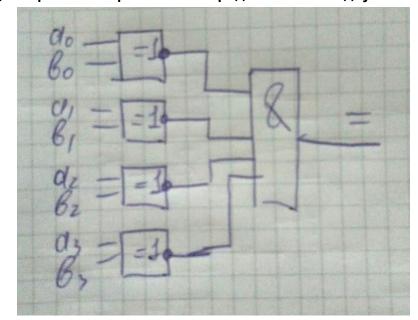

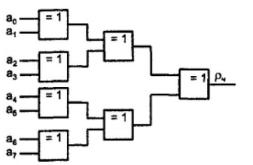

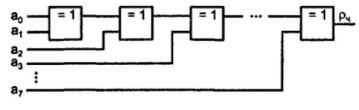

- 13. Привести схемы компаратора равенства двух 4-х разрядных двоичных чисел и схемы свёртки 4-х разрядного двоичного числа пирамидального и последовательного типов. Опишите их функционирование. Сравните быстродействие этих двух типов схем свертки.

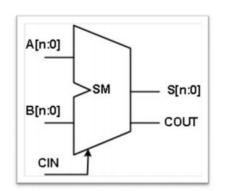

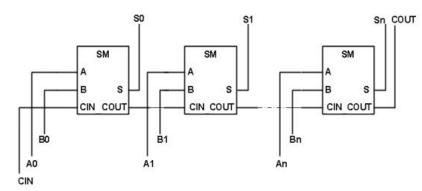

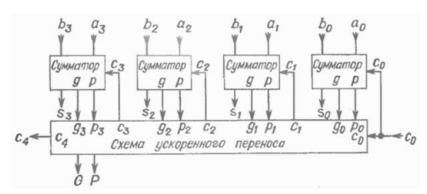

- 14. Описать функцию и привести схему одноразрядного сумматора. Привести логическую схему 4-х разрядного сумматора с последовательным переносом и описать ее «внутреннее» функционирование.

| тэ. Описать функцию и привести схему одноразрядного сумматора. Привести логическую схему 3-х разрядного сумматора с параллельным переносом и описать ее «внутреннее» функционирование.                                                                                                                                                                              | 18       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 16. Привести условное обозначение, таблицу истинности и схему комбинационного сдвигателя на 03 разряда. Описать «внутреннее» функционирование схемы.                                                                                                                                                                                                                | 18       |

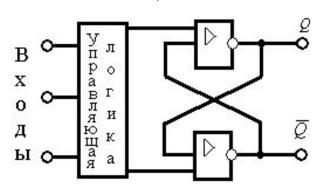

| 17. Привести классификацию триггеров с описанием особенностей каждого класса. Привести обобщенную структурную схему триггера                                                                                                                                                                                                                                        | 20       |

| 18. Описать и показать на временной диаграмме отличия функционирования D-триггера- защелки (latch) и синхронного «по фронту» D-триггера. Какой из эт типов триггеров находит наибольшее применение в электронной вычислительной технике и почему?                                                                                                                   | их<br>21 |

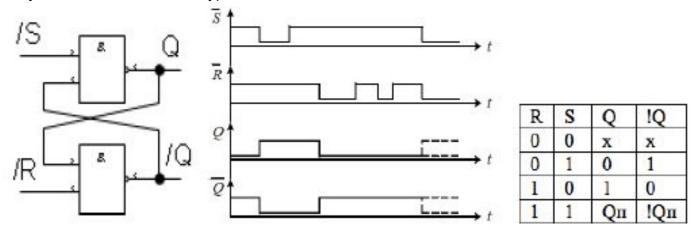

| 19. Привести схему и описать функционирование асинхронного RS-триггера на базе элементов ИЛИ-НЕ. Поясните функционирование на временной диаграмм Какая логика информационных сигналов (ПОЗИТИВНАЯ или НЕГАТИВНАЯ) характерна для этой схемы?                                                                                                                        |          |

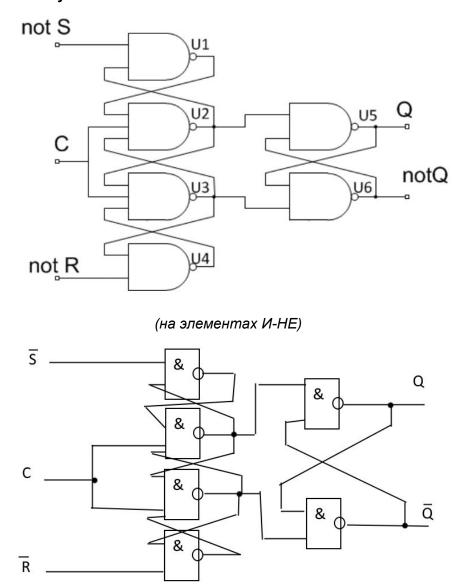

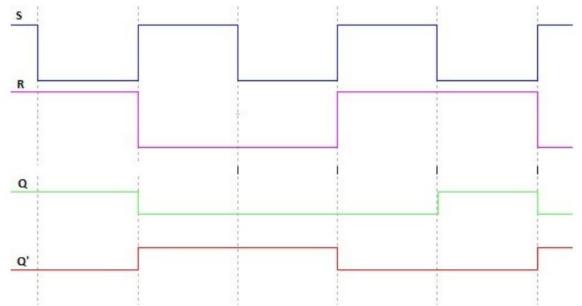

| 20. Привести схему и описать функционирование асинхронного RS-триггера на базе элементов И-НЕ. Поясните функционирование на временной диаграмме. Какая логика информационных сигналов (ПОЗИТИВНАЯ или НЕГАТИВНАЯ) характерна для этой схемы?                                                                                                                        | a<br>23  |

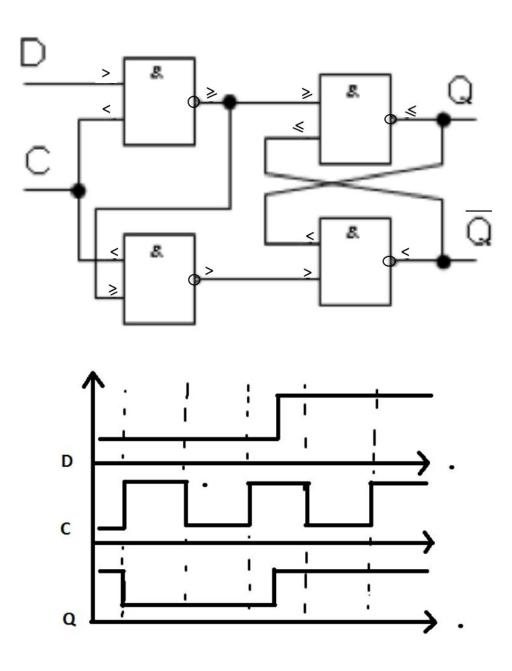

| 21. Привести схему и описать функционирование D-триггера-защелки (latch), построенного на базе элементов И-НЕ. Поясните функционирование на временной диаграмме входных и выходных сигналов.                                                                                                                                                                        | 24       |

| 22. Привести схему и описать функционирование синхронного JK-триггера с управлением уровнем синхросигнала, построенного на базе элементов И-НЕ. Почему возникают ограничения на длительность синхроимпульса, характерны для этой схемы? Как элементы задержки помогают уменьшить эти ограничени 25                                                                  |          |

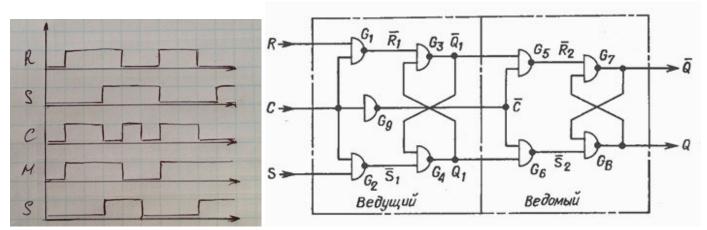

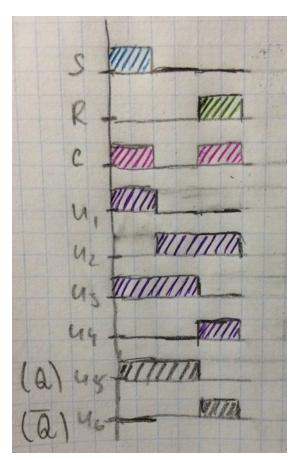

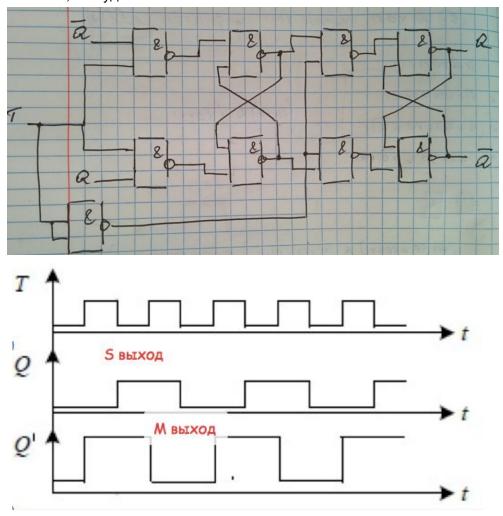

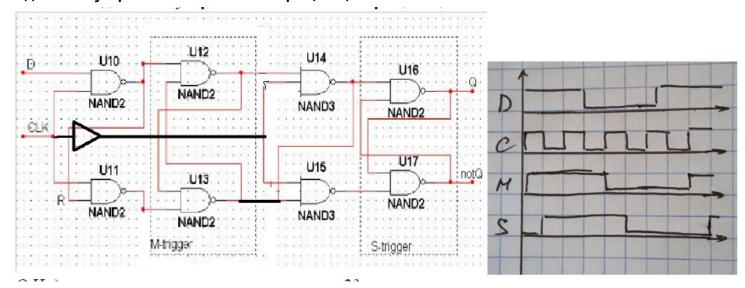

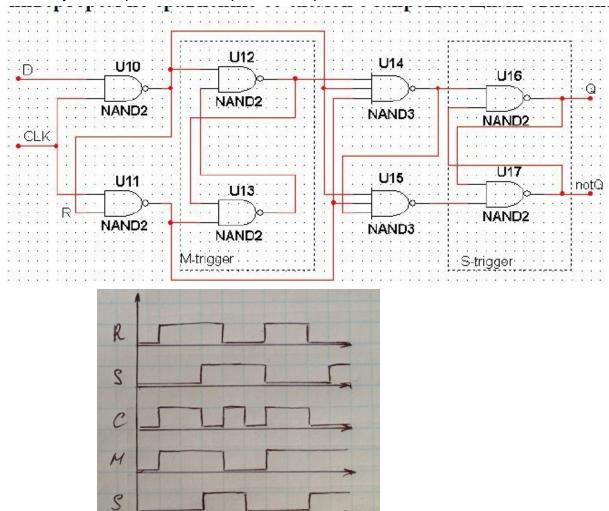

| 23. Привести схему и описать функционирование синхронного RS-триггера, построенного по схеме MS-триггера с инвертором. Покажите на общей временной диаграмме изменение состояний входных сигналов, выходов М-триггера и выходов S-триггера. В чем состоит недостаток схемы MS-триггер инвертором, как этот недостаток устраняется в схеме с запрещающими связям 26  |          |

| 24. Привести схему и описать функционирование синхронного RS-триггера с динамическим управлением записью (универсальная трехтриггерная ячейка). Покажите на временной диаграмме изменение состояний входных сигналов, выходов триггеров 1-й ступени и выходов триггера 2-й ступени.                                                                                 | 27       |

| 25. Привести схему и описать функционирование синхронного Т-триггера, построенного по схеме MS-триггера с запрещающими связями. Покажите на временной диаграмме изменение состояний входных сигналов, выходов М-триггера и выходов S-триггера. В чем состоит преимущество схемы MS-триггера с запрещающими связями по сравнению со схемой MS-триггера с инвертором. | :<br>29  |

| 26. Привести схему и описать функционирование синхронного D-триггера на базе MS-триггера с инвертором. Для демонстрации функционирования                                                                                                                                                                                                                            |          |

MS-триггера покажите на временной диаграмме изменение состояний входных сигналов MS-триггера, выходов M-триггера и выходов S-триггера. В чем состоит недостаток схемы MS-триггера с инвертором, как этот недостаток устраняется в

30

схеме с запрещающими связями.

| 27. Привести схему и описать функционирование синхронного D-триггера на базе MS-триггера с запрещающими связями. Для демонстрации функционирования MS-триггера покажите на временной диаграмме изменение состояний входных сигналов MS-триггера, выходов M-триггера и выходов S-триггера. В чем состоит недостаток схемы MS-триггера с инвертором по                                                  |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| сравнению со схемой с запрещающими связями.                                                                                                                                                                                                                                                                                                                                                           | 31        |

| 28. Привести схему и описать функционирование синхронного JK-триггера на базе MS-триггера с инвертором. Для демонстрации функционирования MS-триггера покажите на временной диаграмме изменение состояний входных сигналов MS-триггера, выходов М-триггера и выходов S-триггера. В чем состо недостаток схемы MS-триггера с инвертором, как этот недостаток устраняется схеме с запрещающими связями. | ит        |

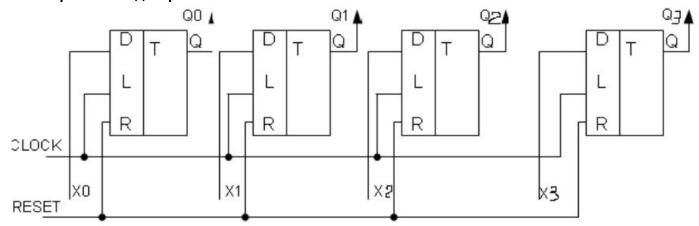

| 29. Приведите схему и опишите функционирование 4-х разрядного накопительного регистра-защелки с асинхронным сбросом, построенного на D-триггерах. Продемонстрируйте это на временной диаграмме.                                                                                                                                                                                                       | 33        |

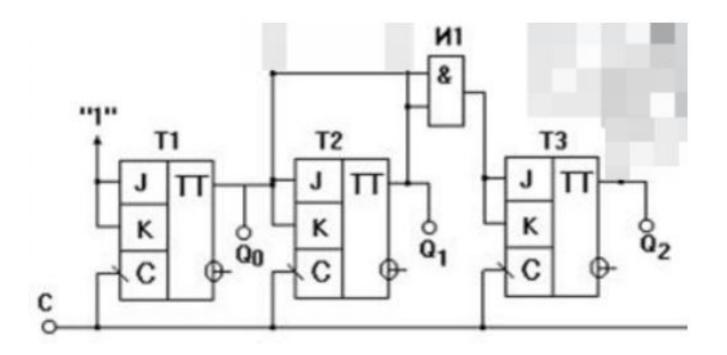

| 30. Приведите схему, опишите функционирование и нарисуйте временную диаграмму сигналов для двоичного 3-х разрядного счетчика с последовательным переносом и непосредственными связями между разряда построенного на синхронных D-триггерах.                                                                                                                                                           | ми,<br>34 |

| 31. Приведите схему, опишите функционирование и нарисуйте временную диаграмму сигналов для двоичного 3-х разрядного счетчика со сквозным переносом между разрядами, построенного на синхронных Т-триггерах.                                                                                                                                                                                           | 35        |

| 32. Приведите схему, опишите функционирование и нарисуйте временную диаграмму сигналов для двоичного 3-х разрядного синхронного счетчика с параллельным переносом между разрядами, построенного на синхронных JK-триггерах.                                                                                                                                                                           | 37        |

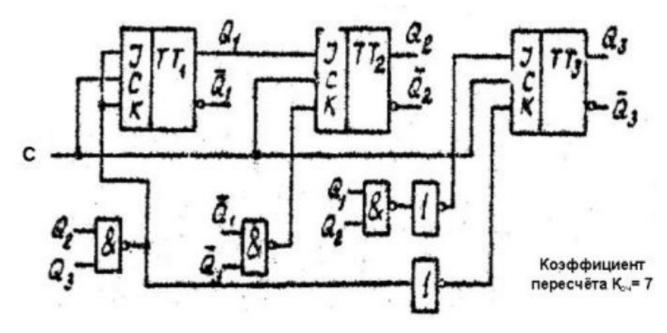

| 33. Приведите схему, опишите функционирование и нарисуйте временную диаграмму сигналов для двоичного 3-х разрядного счетчика с параллельным переносом между разрядами, с коэффициентом пересчета K=7, построенного синхронных JK-триггерах.                                                                                                                                                           | на<br>39  |

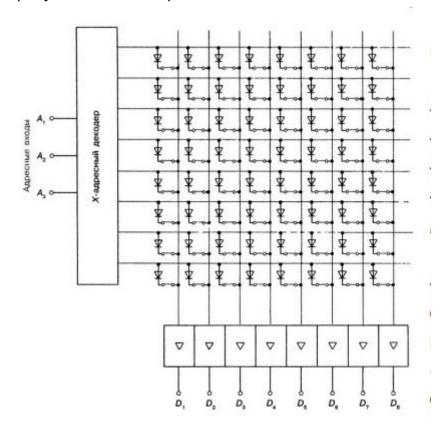

| 34. Нарисуйте схему ПЗУ с диодными элементами. Поясните, как в ячейку памя записать «1» и «0» и опишите по схеме функционирование памяти в режиме чтения?                                                                                                                                                                                                                                             | яти<br>40 |

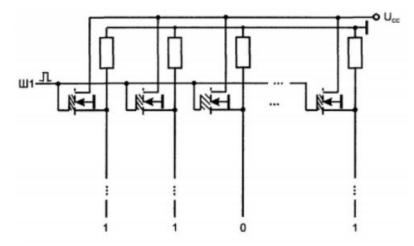

| 35. Нарисуйте схему масочного ПЗУ с транзисторными элементами. Поясните, как в ячейку памяти записать «1» и «0» и опишите по схеме функционирование памяти в режиме чтения?                                                                                                                                                                                                                           |           |

| 36. Что такое репрограмируемое ПЗУ (РППЗУ)? Покажите конструкцию ЛИЗМОП-транзистора и схему ячейки РППЗУ на ЛИЗМОП-транзисторе. По этим схемам объясните, как происходит запись и стирание информации (значений лог.«1» и лог.«0») в ячейки памяти данного типа.                                                                                                                                      | 42        |

| 37. Что такое репрограмируемое ПЗУ (РППЗУ)? Покажите конструкцию МНОП-транзистора и схему ячейки РППЗУ на МНОП-транзисторе. По этим схемам объясните, как происходит запись и стирание информации (значений лог.«1» и лог.«0») в ячейки памяти данного типа.                                                                                                                                          | 43        |

|                                                                                                                                                                                                                                                                                                                                                                                                       |           |

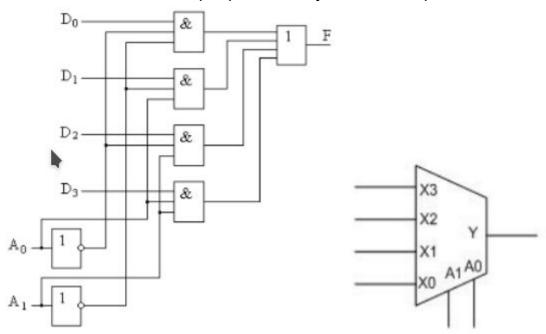

1. Описать функцию мультиплексора. Привести условное обозначение, таблицу истинности и логическую схему одноразрядного мультиплексора «4-в-1», описать «внутреннее» функционирование схемы.

Мультиплексор (multiplexer) – комбинационный БОЭ который осуществляет коммутацию одного из нескольких цифровых входов на один выход (говорят: «мультиплексор n в 1»). Номер подключенного входа задается двоичным кодом на специальном k-разрядном адресном входе n max =2 k.

Логическая схема одноразрядного мультиплексора "4-в-1"

Функционирование схемы: Исходя из значений сигналов А1 и А0 на выходе Ү будет значение соответственно таблице истинности.

#### Таблица истинности

| A1 | A0 | X3  | X2  | X1  | X0  | Y  |

|----|----|-----|-----|-----|-----|----|

| 0  | 0  | 0/1 | 0/1 | 0/1 | 0/1 | X0 |

| 0  | 1  | 0/1 | 0/1 | 0/1 | 0/1 | X1 |

| 1  | 0  | 0/1 | 0/1 | 0/1 | 0/1 | X2 |

| 1  | 1  | 0/1 | 0/1 | 0/1 | 0/1 | X3 |

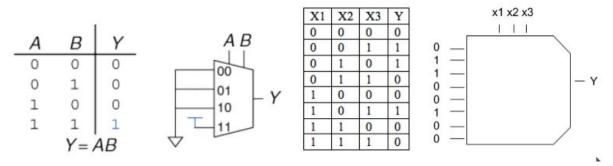

2. Описать функцию мультиплексора. Описать способ реализации произвольной логической функции при помощи мультиплексора. Привести схему, реализующую указанную ниже логическую функцию и описать ее работу:

$$Y = (\overline{x1} \cdot \overline{x2} \cdot x3) + (x1 \cdot \overline{x2} \cdot x3) + (\overline{x1} \cdot x2 \cdot \overline{x3})$$

Функция мультиплексора — выбрать одно из входных значений в зависимости от значения сигнала сигнала. Мультиплексоры могут использоваться как таблицы преобразования ( lookup tables ) для выполнения логических функций. Чтобы реализовать при помощи мультиплексора произвольную логическую функцию можно входы мультиплексора подключить 0 и 1 согласно соответствующей строке таблицы истинности, а входы А и В будут служить управляющими линиями. Например, при помощи мультиплексора получить двухвходовой элемент И:

Данную функцию можно реализовать на мультиплексоре 8-в-1

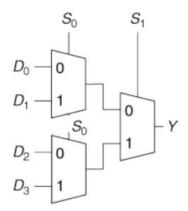

3. Описать функцию мультиплексора. Привести и описать функционирование схемы мультиплексора «4-в-1», построенной на нескольких мультиплексорах «2-в-1».

Функция мультиплексора — выбрать одно из входных значений в зависимости от значения управляющего сигнала.

Мультиплексоры, управляемые сигналом S0, будут определять, из какой пары битов выбирать значение - из младшей или из старшей. Мультиплексор, управляемый сигналом S1, будет определять, какое из значений (младшее или старшее) выбранной пары подавать на выход.

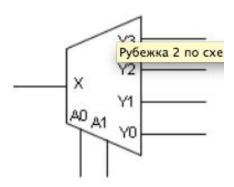

4. Описать функцию демультиплексора. Привести условное обозначение, таблицу истинности и логическую схему одноразрядного демультиплексора «1-в-4», описать «внутреннее» функционирование схемы.

Демультиплексор - комбинационный БОЭ по функции обратный мультиплексору: осуществляет коммутацию одного цифрового входа на один из нескольких цифровых выходов (говорят: «демультиплексор 1вп»). Номер подключенного выхода задается двоичным кодом на специальном k-разрядном адресном входе n max =2 k. Функция демультиплексора — переключения сигнала с одного информационного входа на один из информационных выходов.

Условное обозначение

#### Таблица истинности

| A1 | A0 | X   | Y3 | Y2 | Y1 | Y0 |

|----|----|-----|----|----|----|----|

| 0  | 0  | 0/1 | 0  | 0  | 0  | X  |

| 0  | 1  | 0/1 | 0  | 0  | X  | 0  |

| 1  | 0  | 0/1 | 0  | X  | 0  | 0  |

| 1  | 1  | 0/1 | X  | 0  | 0  | 0  |

#### Логическая схема

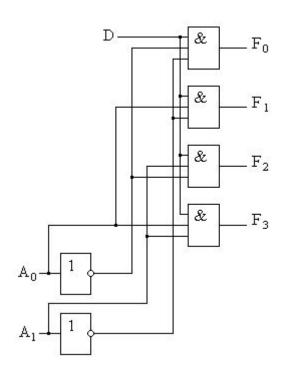

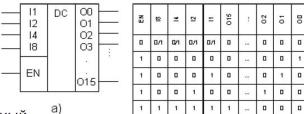

5. Описать функцию двоичного дешифратора. Привести условное обозначение, таблицу истинности и логическую схему двоичного дешифратора 2-х разрядного двоичного кода. Описать «внутреннее» функционирование схемы.

<u>Дешифратор</u>–комбинационный БОЭ который преобразует входной код в отличный от него выходной код с равным или большим количеством разрядов. <u>Двоичный дешифратор (полный)</u> –преобразует К-разрядное двоичное число в 2К-разрядный унитарный код (код «1 из N»).

### Дешифратор: обозначение и схема

**{I8,I4,I2,I1}** – входной четырехразрядный двоичный код;

**{O15,O14,..., O0}** – выходной унитарный код. **EN (ENABLE)** – вход разрешения преобразования: дешифратор выполняет преобразование только, если на входе EN активный уровень («EN» = 1 или «not EN» = 0). При неактивном уровне на выходах все «0». Примеры:

EN=1 I = {0101} => O={0000000000100000} EN=1 I = {0111} => O={0000000010000000} EN=0 I = {0101} => O={0000000000000000} EN=0 I = {0111} => O={00000000000000000}

Функция двоичного дешифратора — преобразование К-разрядного двоичного числа в 2 К-разрядный унитарный код(код «1 из N»). Если N = 2<sup>K</sup>, то каждому варианту выходного кода соответствует свой выходной код; такой дешифратор именуется полным. При N < 2<sup>K</sup> дешифратор неполный.

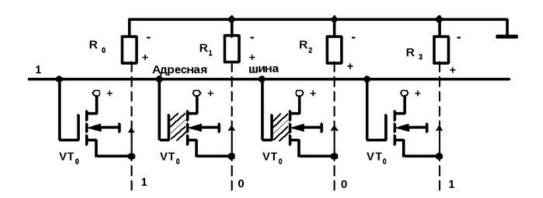

6. Описать функцию двоичного дешифратора. Привести схему подключения дешифратора «2-в-4» в качестве селектора адреса для 4-х устройств памяти, подключенных к общей шине (данных) ЭВМ, и описать функционирование этой схемы.

Функция двоичного дешифратора — преобразование К-разрядного двоичного числа в 2<sup>K</sup>-

разрядный унитарный код(код «1 из N»).

Унитарный означает такой способ представления числа, при котором величина числа определяется положением активного сигнала на множестве выходов. Двоичное число, подаваемое на информационные входы, указывает номер того выхода, на котором наблюдается активный сигнал. То есть входы дешифратора в данном случае являются адресными, определяют адрес выхода с активным сигналом.

Схема подключения в качестве селектора адреса устройств

Задача селектора адреса – выдавать управляющий сигнал только в пределах выбранного диапазона.

В зависимости от значения на ША будет активирована лишь одна схема памяти (МЕМ).

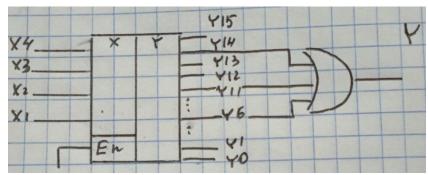

7. Описать функцию двоичного дешифратора. Описать способ реализации произвольной логической функции с использованием дешифратора и логического элемента ИЛИ. Привести схему, реализующую приведенную ниже логическую функцию и описать ее работу: Y=(! x 1· x 2· x 3·! x 4) + ( x 1·! x 2· x 3· x 4) + ( x 1·x 2· x 3·! x 4)

Функция двоичного дешифратора — преобразование К-разрядного двоичного числа в 2<sup>^</sup>K-разрядный унитарный код(код «1 из N»).

Дешифратор может комбинироваться с элементами ИЛИ для построения логических функций,поскольку каждый выход дешифратора представляет одиночный минитерм. При реализации функции на дешифраторах нужно записать функцию в виде ТИ или в ДНФ по очевидным причинам. N-входовая функция может быть реализована на дешифраторах (из N входов получем 2^N выходов) и М-выходом элементе ИЛИ (М — число минитермов).

|    |    |    |    | - |

|----|----|----|----|---|

| X1 | X2 | X3 | X4 | Y |

| 0  | 0  | 0  | 0  | 0 |

| 0  | 0  | 0  | 1  | 0 |

| 0  | 0  | 1  | 0  | 0 |

| 0  | 0  | 1  | 1  | 0 |

| 0  | 1  | 0  | 0  | 0 |

| 0  | 1  | 0  | 1  | 0 |

| 0  | 1  | 1  | 0  | 1 |

| 0  | 1  | 1  | 1  | 0 |

| 1  | 0  | 0  | 0  | 0 |

| 1  | 0  | 0  | 1  | 0 |

| 1  | 0  | 1  | 0  | 0 |

| 1  | 0  | 1  | 1  | 1 |

| 1  | 1  | 0  | 0  | 0 |

| 1  | 1  | 0  | 1  | 0 |

| 1  | 1  | 1  | 0  | 1 |

| 1  | 1  | 1  | 1  | 0 |

Для реализации функции нужен дешифратор 4-16. Так как каждый выход дешифратора Y\_0 - Y\_15 представляет собой терм, то очевидно, что данная функция реализуется путём применения функции ИЛИ на нужных выходах дешифратора, а именно Y\_6, Y\_11, Y\_14.

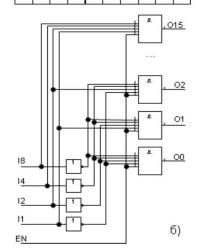

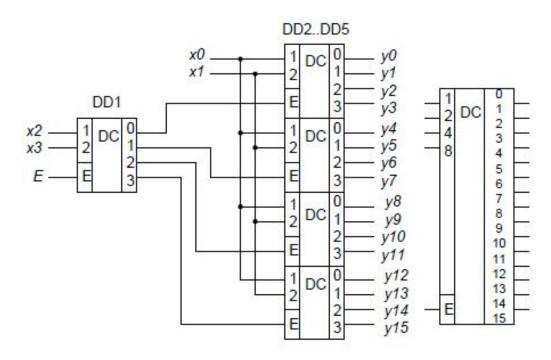

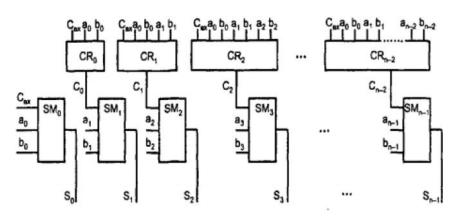

8. Описать функцию двоичного дешифратора. Привести и описать функционирование схемы наращивания размерности дешифратора: из нескольких двоичных дешифраторов «2-в-4» построить двоичный дешифратор «4-в-16».

Функция двоичного дешифратора — преобразование К-разрядного двоичного числа в 2<sup>K</sup>- разрядный унитарный код(код «1 из N»).

Для наращивания размерности используется следующий алгоритм. Входное слово делится на поля, разрядность младших разрядов которых соответствует числу входов дешифраторов. Оставшееся поле старших разрядов служит для получения сигналов разрешения работы одного из последующих дешифраторов.

Пусть в нашем распоряжении имеются полные (число выходов равно  $2^n$  при n информационных входах) дешифраторы типа  $2\rightarrow 4$  (два входа – четыре выхода). Необходимо построить дешифратор, который имеет 4 информационных входа и 16 выходов, то есть дешифратор типа  $4\rightarrow 16$ . В зависимости от состояний сигналов x3 и x2 при наличии на входе разрешения работы E дешифратора DD1 формируется единица на одном из четырёх выходов этого дешифратора. Это приводит к тому, что только один из выходных дешифраторов будет реагировать на комбинацию сигналов на входах x0 и x1. Только выбранный дешифратор сформирует единицу на одном из своих выходов, номер которого определяется сигналами x0 и x1.

Например, пусть на входах x3x2x1x0 присутствует число 1011. На входах x3x2 присутствует комбинация 10, что соответствует в десятичном виде числу 2. Следовательно, именно на выходе 2 дешифратора DD1 сформируется активный сигнал, равный единице. Только дешифратору DD4, который принимает по входу Е активный уровень, будет разрешаться работа. На входах x1x0 присутствует число 11, что соответствует в десятичном виде числу 3. На третьем выходе выбранного дешифратора DD4 будет формироваться единица, то есть активный сигнал. На остальных выходах выбранного дешифратора будет присутствовать нуль так же, как и на выходах невыбранных дешифраторов DD2, DD3, DD5. То есть только на выходе y11 присутствует активный сигнал. Если перевести заданное двоичное число 1011 в десятичную систему, то получим номер выбранного выхода в десятичной системе: 11. 1011\_2=2^3+2^1+2^0=11.

9. Описать функцию двоичного бесприоритетного шифратора и двоичного приоритетного шифратора. Привести условное обозначение двоичного шифратора «4-в-2». Привести таблицу истинности двоичного приоритетного шифратора «4-в-2». Привести схему селектора приоритетов запросов прерываний на базе приоритетного двоичного шифратора.

Двоичные шифраторы преобразуют унарный код ( 1 в N ) в двоичный. При возбуждении одного из входов шифратора на его выходе формируется двоичный код номера возбуждённой входной линии. Полный двоичный шифратор имеет 2<sup>n</sup> входов и п выходов.

Неприоритетный Ш осуществляет преобразование десятичного номера активного входа в двоичный эквивалент этого номера. В приоритетном Ш производится преобразование максимального десятичного номера активного входа в двоичный эквивалент этого номера. Для такого Ш входные сигналы, лежащие снизу от единичной диагонали, по определению не известны ("х" может быть 0 или 1).

| Nº | X_6 | X_5 | X_4 | X_3 | X_2 | X_1 | X_0 | A_2 | A_1 | A_0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 1  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 1   |

| 2  | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 1   | 0   |

| 3  | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 1   | 1   |

| 4  | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 1   | 0   | 0   |

| 5  | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 1   | 0   | 1   |

| 6  | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 0   |

| 7  | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   |

| номер<br>входа | входы<br>x0 x1 x2 x3 |   |   |   | вы<br>у1 | ходы<br>у0 |

|----------------|----------------------|---|---|---|----------|------------|

| 0              | 1                    | 0 | 0 | 0 | 0        | 0          |

| 1              | ō                    | 1 | Ō | ŏ | Ō        | 1          |

| 2              | 0                    | 0 | 1 | 0 | 1        | 0          |

| 3              | 0                    | 0 | 0 | 1 | 1        | 1          |

номер входы выходы входа  $\times 0$ ×1 ×2 ×3 y1 y0 1 0 0 0 0 1 0 0 0 1 1 Х 2 1 0 1 0 X X 3 1 1 1

Рис.20. Рис.21. рис.20 - неприоритетный ш

рис.21 - приоритетный ш

#### Схема селектора приоритетов запросов

addr - адрес

10. Привести условное обозначение, таблицу истинности и логическую схему полного компаратора по величине («больше-меньше-равно») для 2-х разрядных двоичных чисел. Описать «внутреннее» функционирование схемы.

Компараторы определяют отношения между двумя словами. В общем случае компаратор параллельных кодов двух m-разрядных двоичных чисел представляет собой комбинационную схему с 2m входами и тремя выходами. При поступлении на входы кодов двух сравниваемых чисел сигнал логической единицы появляется только на одном из выходов. В некоторых случаях компаратор может иметь менее трех выходов.

Условное обозначение

Логическая схема

#### Таблица истинности

| a1 | a0 | b1 | b0 | a <b< th=""><th>a=b</th><th>a&gt;b</th></b<> | a=b | a>b |

|----|----|----|----|----------------------------------------------|-----|-----|

| 0  | 0  | 0  | 0  | 0                                            | 1   | 0   |

| 0  | 0  | 0  | 1  | 1                                            | 0   | 0   |

| 0  | 0  | 1  | 0  | 1                                            | 0   | 0   |

| 0  | 0  | 1  | 1  | 1                                            | 0   | 0   |

| 0  | 1  | 0  | 0  | 0                                            | 0   | 1   |

| 0  | 1  | 0  | 1  | 0                                            | 1   | 0   |

| 0  | 1  | 1  | 0  | 1                                            | 0   | 0   |

| 0  | 1  | 1  | 1  | 1                                            | 0   | 0   |

| 1  | 0  | 0  | 0  | 0                                            | 0   | 1   |

| 1  | 0  | 0  | 1  | 0                                            | 0   | 1   |

| 1  | 0  | 1  | 0  | 0                                            | 1   | 0   |

| 1  | 0  | 1  | 1  | 1                                            | 0   | 0   |

| 1  | 1  | 0  | 0  | 0                                            | 0   | 1   |

| 1  | 1  | 0  | 1  | 0                                            | 0   | 1   |

| 1  | 1  | 1  | 0  | 0                                            | 0   | 1   |

| 1  | 1  | 1  | 1  | 0                                            | 1   | 0   |

11. Привести схему полного компаратора по величине («больше-меньше-равно») для двух 2-х разрядных двоичных чисел, построенную на базе мультиплексора (-ов). Реализация входов наращивания разрядности компаратора НЕ требуется.

12. Привести схему вычисления бита чётности для 4-х разрядного двоичного слова, построенную на базе 2-х разрядных (2 входа) двоичных дешифраторов.

| a0 | a1 | a2 | а3 | р |

|----|----|----|----|---|

| 0  | 0  | 0  | 0  | 1 |

| 0  | 0  | 0  | 1  | 0 |

| 0  | 0  | 1  | 0  | 0 |

| 0  | 0  | 1  | 1  | 1 |

| 0  | 1  | 0  | 0  | 0 |

| 0  | 1  | 0  | 1  | 1 |

| 0  | 1  | 1  | 0  | 1 |

| 0  | 1  | 1  | 1  | 0 |

| 1  | 0  | 0  | 0  | 0 |

| 1  | 0  | 0  | 1  | 1 |

| 1  | 0  | 1  | 0  | 1 |

| 1  | 0  | 1  | 1  | 0 |

| 1  | 1  | 0  | 0  | 1 |

| 1  | 1  | 0  | 1  | 0 |

| 1  | 1  | 1  | 0  | 0 |

| 1  | 1  | 1  | 1  | 1 |

13. Привести схемы компаратора равенства двух 4-х разрядных двоичных чисел и схемы свёртки 4-х разрядного двоичного числа пирамидального и последовательного типов. Опишите их функционирование. Сравните быстродействие этих двух типов схем свертки.

Схема свертки пирамидального типа

Схема свертки последовательного типа

#### Функционирование:

-пирамидальная - на входы схемы подаем попарно биты одинаковой разрядности на соответствующие элементы ХОР; далее формируется признак четности для каждой входной пары; далее формируется признак четности второго уровня на основе первого уровня и т.д.

-<u>последовательная</u> - на N-ый элемент схемы подаётся результат предыдущей XOR-проверки и  $a_{N-\mathrm{bi} \check{\mathsf{n}}}$  бит

Чаще всего <u>оптимально использовать пирамидальный тип свертки</u>, так как она сориентирована на параллельную работу, а оттого выигрывает по времени.

Для последовательных данных, когда слова передаются по одной линии разряд за разрядом, <u>целесообразно применять схему свертки</u>, которая выдает результат через одну задержку после поступления разряда.

14. Описать функцию и привести схему одноразрядного сумматора. Привести логическую схему 4-х разрядного сумматора с последовательным переносом и описать ее «внутреннее» функционирование.

Полный одноразрядный сумматор - имеет выходы A, B и дополнительный вход CIN (Carry Input) переноса из младшего разряда в многоразрядном сумматоре.

Условное обозначение на функциональнологических схемах

<u>Схема с последовательным переносом:</u> простая схема, но большая задержка распространения переноса через все разряды:  $\mathbf{t_{p\ cr}} = \mathbf{2^*t_{p\ le}}^*\mathbf{n}$

Одноразрядный сумматор (без переноса, полусумматор):

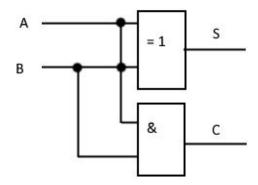

15. Описать функцию и привести схему одноразрядного сумматора. Привести логическую схему 3-х разрядного сумматора с параллельным переносом и описать ее «внутреннее» функционирование.

Одноразрядный сумматор (без переноса, полусумматор):

Схема с параллельным переносом: минимальная задержка распространения переноса вне зависимости от разрядности t\_p\_cr=2...3, но объемная схема формирования переносов.

Отличие параллельного переноса в том, что carry-биты вычисляются сразу, на основе входных данных.

НЕ РИСОВАТЬ ЧЕТВЁРТЫЙ СУММАТОР, ТАК КАК НАМ НУЖЕН ТРЁХРАЗРЯДНЫЙ!

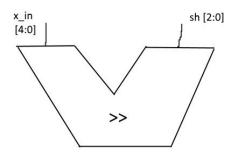

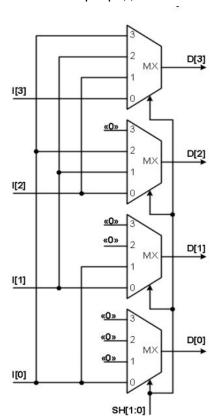

16. Привести условное обозначение, таблицу истинности и схему комбинационного сдвигателя на 0..3 разряда. Описать «внутреннее» функционирование схемы.

Комбинационные схема сдвига (shifter) - БОЭ, построенные на базе мультиплексоров (или аналогичной логики), выполняющие сдвиг многоразрядного входного кода на заданное число разрядов.

Условное обозначение:

Табл истинности:

| 10 | I1 | 12 | 13 | SH0 | SH1 | D0 | D1 | D2 | D3 |

|----|----|----|----|-----|-----|----|----|----|----|

| Α  | В  | С  | D  | 0   | 0   | Α  | В  | С  | D  |

| Α  | В  | С  | D  | 0   | 1   | 0  | Α  | В  | С  |

| Α  | В  | С  | D  | 1   | 0   | 0  | 0  | Α  | В  |

| Α  | В  | С  | D  | 1   | 1   | 0  | 0  | 0  | Α  |

На рисунке - пример схемы сдвига влево на 0..3 разряда

## 17. Привести классификацию триггеров с описанием особенностей каждого класса. Привести обобщенную структурную схему триггера

Триггеры можно классифицировать по четырем направлениям: по логике работы, по способу синхронизации, по внутренней структуре, по схемотехнике.

- 1. <u>Логика работы</u> правила переключения триггера под воздействием входных управляющих сигналов:

- RS-триггер с раздельными входами «установки» (записи «1», вход S(et)) и «сброса» (записи «0», сигнал R(eset)).

- D- триггер (от Delay) задержки информационного сигнала.

- Т-триггер (от Tact) тактируемый или счетный триггер.

- JK-триггер (от Jump-Kill) универсальный триггер, который может быть сконфигурирован как RS- или Т-триггер.

- комбинированный например, RST-триггер: тактируемый со входами «установки» и «сброса».

- со сложной логикой с группами входов, связанных логическими зависимостями. Например, ЈК-триггер с 3-я входами Ј и 3-я К, связанными конъюнкцией: (J1/J2/J3)и(K1/K2/K3).

- 2. <u>Асинхронные</u> (нетактируемые) переключение одновременно с появлением соответствующей комбинации на управляющих (информационных) входах. <u>Синхронные</u> (тактируемые) переключение при наличии соответствующей управляющей комбинации, но только по сигналу (фронту или уровню) на специальном тактовом (синхронизации) входе (С / CLK / CLOCK).

- Синхронные управляемые уровнем при одном уровне тактового сигнала триггер воспринимает состояние управляющих входов, а при другом не воспринимает. Например, «триггер-защелка» (latch).

- Синхронные управляемые фронтом переходы из состояния в состояние происходят по фронту тактового сигнала. Например, синхронный D-триггер.

- 3. Одноступенчатые одна запоминающая схема. Так строятся асинхронные и синхронные управляемые уровнем триггеры.

<u>Двухступенчатые</u> (или многоступенчатые) - состоят из двух или более одноступенчатых триггеров. Ступени переключаются по очереди. По многоступенчатой схеме строятся синхронные управляемые фронтом триггеры - наиболее применяемый сегодня тип триггеров.

- Триггеры на базе дискретных элементов (резисторов, конденсаторов, транзисторов)

- Триггеры на базе цифровых элементов (И- НЕ, ИЛИ-НЕ и т.п.)

Обобщенная схема:

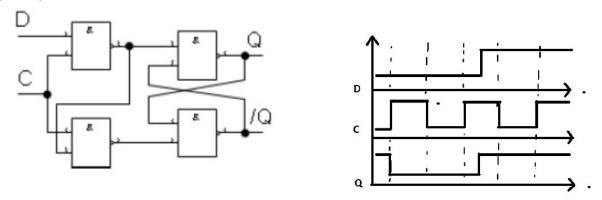

18. Описать и показать на временной диаграмме отличия функционирования D-триггеразащелки (latch) и синхронного «по фронту» D-триггера. Какой из этих типов триггеров находит наибольшее применение в электронной вычислительной технике и почему?

D-триггер с управлением по уровню, так же называется «триггер-защелка» (LATCH) - повторяет

вход D при активном уровне на C и удерживает на выходе последнее значение с входа D при переключении C в неактивное состояние.

Второй тип, наиболее часто используемый - D-триггер с управлением по фронту синхросигнала,

так называемый FLIP-FLOP. Данные записываются в него в момент перепада синхросигнала и

сохраняются неизменными до следующего фронта.

(в этом примере <u>задний фронт</u> т.е. <u>спад</u>)

Синхронные управляемые фронтом триггеры - наиболее применяемый сегодня тип триггеров.

У триггеров с синхронизацией по уровню сигнала есть один недостаток — изменение входных сигналов и их возвращение в исходное положение может происходить во время разрешения тактирующим сигналом, что приведет к тому, что выход схемы насквозь просматривает вход в течении некоторого интервала времени. И следовательно схемы построенные на синх. по фронту более устойчивы к шумам и помехам.

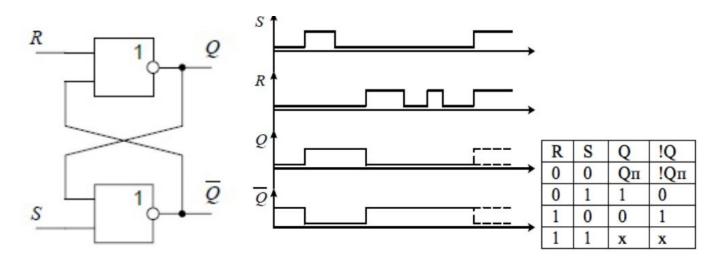

# 19. Привести схему и описать функционирование асинхронного RS-триггера на базе элементов ИЛИ-НЕ. Поясните функционирование на временной диаграмме. Какая логика информационных сигналов (ПОЗИТИВНАЯ или НЕГАТИВНАЯ) характерна для этой схемы?

Асинхронный RS-триггер – имеет два независимых входа управления «Установка» (Set) и «Сброс» (Reset), часто используется как схема памяти в более сложных типах триггеров. На входах S и R может быть четыре комбинации набора нулей и единиц.

Если на обоих входах присутствует уровень логического нуля (не активный уровень), то состояние выходов триггера остается неизменным. При подаче на вход установки S логической единицы триггер устанавливается в единичное состояние (на выходе Q устанавливается уровень логической единицы, а на выходе !Q – уровень логического нуля). При подаче навход сброса R логической единицы триггер переключается (на выходе Q –уровень логической единицы). Если на оба входа подать активный уровень логической единицы, то состояние триггера будет не определено. Эта комбинация является запрещенной.

Позитивная логика информационных сигналов характерна для этой схемы, т.к. уровень лог.единицы является активным уровнем.

Логика ПОЗИТИВНАЯ (нулевые сигналы ничего не меняют, положительные меняют состояние).

20. Привести схему и описать функционирование асинхронного RS-триггера на базе элементов И-НЕ. Поясните функционирование на временной диаграмме. Какая логика информационных сигналов (ПОЗИТИВНАЯ или НЕГАТИВНАЯ) характерна для этой схемы?

На входах S и R может быть четыре комбинации набора нулей и единиц. Если на обоих входах

присутствует уровень логической единицы (не активный уровень), то состояние выходов триггера

остается неизменным. При подаче на вход установки S логического нуля триггер устанавливается

в единичное состояние (на выходе Q устанавливается уровень логической единицы, а на выходе !Q

– уровень логического нуля). При подаче на вход сброса R логического нуля триггер переключается (на выходе Q –уровень логического нуля, а на выходе !Q –уровень логической

единицы). Если на оба входа подать активный уровень логического нуля, то состояние триггера

будет не определено. Эта комбинация является запрещенной.

Негативная логика информационных сигналов характерна для этой схемы, т.к. уровень лог.нуля является активным уровнем.

Логика НЕГАТИВНАЯ (положительные сигналы ничего не меняют, нулевые меняют).

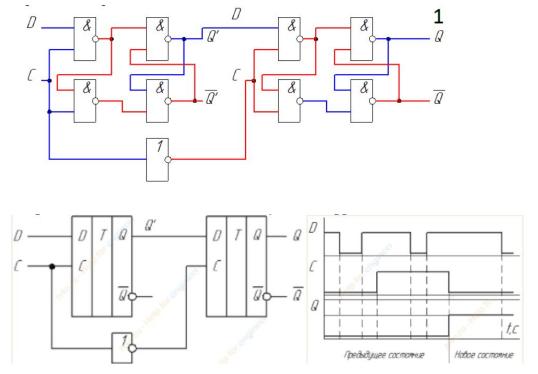

21. Привести схему и описать функционирование D-триггера-защелки (latch), построенного на базе элементов И-НЕ. Поясните функционирование на временной диаграмме входных и выходных сигналов.

Из широко применяемых первый - D-триггер с управлением по уровню, также называемый «триггер-защелка» (LATCH). Он прозрачен для входного информационного сигнала пока сигнал синхронизации (С) в активном состоянии и защелкивает значение на выходе (Q) в момент перехода (С) в неактивное состояние.

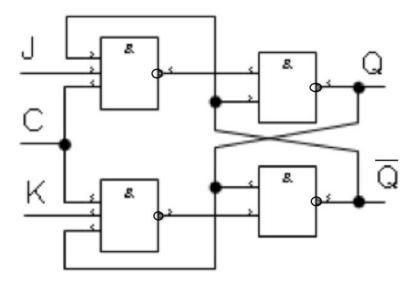

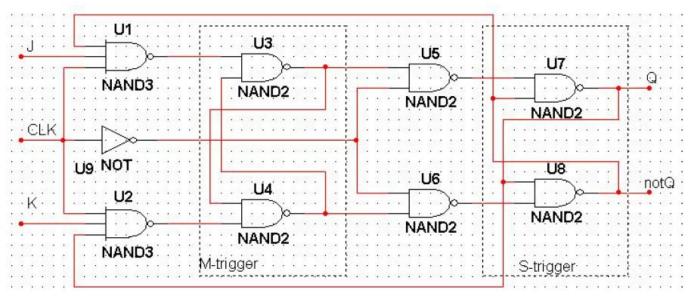

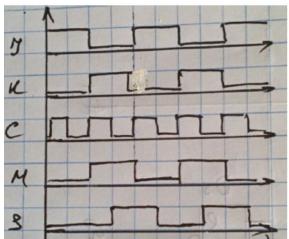

22. Привести схему и описать функционирование синхронного JK-триггера с управлением уровнем синхросигнала, построенного на базе элементов И-НЕ. Почему возникают ограничения на длительность синхроимпульса, характерные для этой схемы? Как элементы задержки помогают уменьшить эти ограничения?

Когда на вход J и К подаются лог. единицы, то схема начинает работать как Т-триггер и меняет свое состояние по импульсу на входе С. И тут создаются такие же проблемы как у Т-триггера: Нужно подавать на вход С сигнал такой по времени, чтобы все элементы успели переключиться только один раз, иначе будет работать как генератор, если импульс будет слишком коротких, то не все лог.элементы переключатся.

K-триггер похож на RS-триггер (вход J эквивалентен входу S , а вход K - входу R ), но не имеет запрещенного состояния K(R)=1, J(S)=1. При условии J=K=1 триггер осуществляет инверсию предыдущего состояния, а при остальных комбинациях входных сигналов функционирует в соответствии с таблицей истинности RS -триггера.

23. Привести схему и описать функционирование синхронного RS-триггера, построенного по схеме MS-триггера с инвертором. Покажите на общей временной диаграмме изменение состояний входных сигналов, выходов M-триггера и выходов S-триггера. В чем состоит недостаток схемы MS-триггера с инвертором, как этот недостаток устраняется в схеме с запрещающими связями.

MS - триггеры содержат в своем составе основной/главный (MASTER) и вспомогательный/подчиненный (SLAVE) - триггеры. Информация заносится в М-триггер по переднему фронту синхроимпульса, а по заднему фронту (по спаду) синхроимпульса переписывается из М-триггера в в S- триггер. В исходном состоянии (C = 0) оба триггера (М и S)находятся в одинаковых состояниях: в них сохраняется информация, записанная по предыдущему синхроимпульсу. При поступлении 18 синхроимпульса (С=1) новая входная информация записывается в М-триггер. При этом состояние S-триггера и, соответственно, значения на выходах схемы остаются неизменными, т.к. он заблокирован низким уровнем сигнала синхронизации S-триггера, поступающим с выхода G9 на входы G5 и G6. По спаду синхроимпульса на входе C (C=0) состояние М-триггера фиксируется и остается неизменным, пока С=0. Это обеспечивается блокирующими элементами G1 и G2. Таким образом, в MS-триггер записывается информация, установленная на информационных входах непосредственно перед спадом сигнхроимпульса. Одновременно с блокировкой М-триггера синхросигнал S-триггера, поступающий с выхода G9 на входы G5 и G6, становится равным «1», что ведет к перезаписи информации с выходов М-триггера в S-триггер. При этом значения на информационных входах MS- триггера R и S могут изменяться как угодно – они не будут восприняты заблокированным М-триггером.

Существенным недостатком триггера с инвертором является возможность возникновения в нем опасных состязаний при больших разбросах времени задержки распространения сигнала логических элементов. Для срабатывания М- и S-триггеров по переднему и заднему фронтам - каждого по своему, в цепи синхросигнала между М- и S-триггерами включается инвертор G9, блокирующий перезапись информации в S - триггер, пока C=1 и выполняется запись в М - триггер. Процесс занесения информации в М-триггер происходит быстрее, чем будут заблокированы элементы D5 и D6 нулевым сигналом, формируемым на выходе инвертора G9. В этом случае возникает опасность того, что вновь поступившая информация будет также занесена в S-триггер во время действия синхроимпульса, а не по его окончании. В схемах Т-триггера и ЈК-триггера в счетном режиме это приводит к преждевременному изменению сигналов обратной связи и новому переключения М-триггера. При работе в составе сдвигающего регистра преждевременное изменение информационных сигналов Q и Q вызывает внесение ложной информации в М -триггер последующего разряда.

От этого недостатка свободен MS-триггер с запрещающими связями, в котором функцию инвертора синхросигнала выполняют элементы D1 и D2. При выработке любым из этих элементов управляющего нулевого сигнала (что означает, что M-триггер должен изменить свое состояние) до переключения M-триггера производится блокировка элементов D5 и D6, чем обеспечивается сохранение ранее занесенной информации в S -триггер. Благодаря этому исключаются условия для возникновения опасных состязаний. В остальном принцип работы рассматриваемой схемы ничем не отличается от принципа работы схемы MS-триггера с инвертором.

24. Привести схему и описать функционирование синхронного RS-триггера с динамическим управлением записью (универсальная трехтриггерная ячейка). Покажите на временной диаграмме изменение состояний входных сигналов, выходов триггеров 1-й ступени и выходов триггера 2-й ступени.

В схеме трехтриггерной ячейки используются три типовых асинхронных RS – триггера, один из которых является основным, и два других – коммутирующими. Коммутирующие триггеры реализованы на элементах D1, D2 и D3, D4, а главный триггер – на элементах D5 и D6. По переднему фронту синхроимпульса на входе С коммутирующие триггеры сохраняют значения со входов notR и notS соответственно.

С выходов коммутирующих триггеров сигналы попадают на входы установки основного триггера (на элементах D5 и D6) и одновременно с этим на входы блокировки противоположного коммутирующего триггера. Соответственно, если активный уровень «0» подан на вход notR, это приведет к блокировке нижнего коммутирующего триггера и, соответственно, к невозможности изменения состояния триггера (в данном примере - его установки), до следующего синхроимпульса.

Возможно там HeS и HeR...С в два раза короче S поэтому на временной диаграмме от него ничего HeS не зависит.

25. Привести схему и описать функционирование синхронного Т-триггера, построенного по схеме MS-триггера с запрещающими связями. Покажите на временной диаграмме изменение состояний входных сигналов, выходов М-триггера и выходов S-триггера. В чем состоит преимущество схемы MS-триггера с запрещающими связями по сравнению со схемой MS-триггера с инвертором.

Схема включает в себя два Т-триггера, управляемых уровнем синхроимпульса: М-триггер (D1,D2,D3,D4) и S-триггер(D5,D6,D7,D8). Информация заноситься в М-триггер по переднему фронту синхроимпульса а по спаду синхроимпульсов – переписывается из М-триггера в S-триггер. Для срабатывания М- и S-триггеров по переднему и по заднему фронту соответственно, в цепи между М- и S-триггерами включается инвентор, блокирующий перезапись информации в S-триггер, пока С=1 и выполняется запись в М-триггер. В исходном состоянии (T=0) в триггерах М и S сохраняется информация, записанная по предыдущему синхроимпульсу. При поступлении синхроимпульса новая входная информация записывается в М-триггер. При этом состояние S-триггера и значения на выходах схемы остаются неизменными, т.к. он заблокирован низким уровнем сигнала синхронизации поступающем с выхода инвентора на входы D5 и D6. По спаду импульса синхронизации на входе Т состояние М-триггера фиксируется и остается неизменным, пока T=0. Это обеспечивается блокирующими элементами D1 и D2. Одновременно с блокировкой М-триггера синхросигнал S-триггера, поступающий с выхода инвентора на входы D5 и D6, становиться равным лог. 1, что ведет к перезаписи информации с выхода М-триггера в S-триггер.

MS-триггер RS-типа легко преобразовать в T-триггер путем подключения выходов Q и notQ ко входам R и S соответственно. Так как схема MS-триггера фактически работает в двухтактном режиме (по фронту и спаду синхроимпульса), то проблем с многократным переключением триггера из за обратных связей, подобных рассмотренным выше T-триггерам управляемых уровнем синхросигнала, не будет.

26. Привести схему и описать функционирование синхронного D-триггера на базе MS-триггера с инвертором. Для демонстрации функционирования MS-триггера покажите на временной диаграмме изменение состояний входных сигналов MS-триггера, выходов М-триггера и выходов S-триггера. В чем состоит недостаток схемы MS-триггера с инвертором, как этот недостаток устраняется в схеме с запрещающими связями.

(вместо треугольничка - инвертор; NAND = И-НЕ)

Недостатком в схеме с инвертором является возможность возникновения в нем опасных состязаний при больших разбросах времени задержки распространения сигнала лог. элементов. Если в схеме например сумма времени задержки элементов D2 и D4 будет больше времени задержки инвертора, то процесс занесения информации в М-триггер происходит быстрее, чем будут заблокированы элементы D5 и D6 нулевым сигналом, формируемым на выходе инвертора. Поэтому возникает опасность того, что вновь поступившая информация будет также занесена в S-триггер во время действия синхроимпульса, а не по его окончании. От этого недостатка свободен МS-триггер с запрещающими связями, в котором функцию инвертора синхросигнала выполняют элементы D1 и D2. При выработке любым из этих элементов управляющего нулевого сигнала до переключения М-триггера производится блокировка элементов D5 и D6, чем обеспечивается сохранение ранее занесенной информации в S-триггер.

27. Привести схему и описать функционирование синхронного D-триггера на базе MS-триггера с запрещающими связями. Для демонстрации функционирования MS-триггера покажите на временной диаграмме изменение состояний входных сигналов MS-триггера, выходов М-триггера и выходов S-триггера. В чем состоит недостаток схемы MS-триггера с инвертором по сравнению со схемой с запрещающими связями.

Функционирование как в прошлых вопросах.

(Reset, Set, CLK, Master, Slave)

Диаграмма -

Недостатком в схеме с инвертором является возможность возникновения в нем опасных состязаний при больших разбросах времени задержки распространения сигнала лог.элементов.

Если в схеме например сумма времени задержки элементов D2 и D4 будет больше времени задержки инвертора, то процесс занесения информации в M-триггер происходит быстрее, чем будут заблокированы элементы D5 и D6 нулевым сигналом, формируемым на выходе инвертора. Поэтому возникает опасность того, что вновь поступившая информация будет также занесена в S-триггер во время действия синхроимпульса, а не по его окончании.

От этого недостатка свободен MS-триггер с запрещающими связями, в котором функцию инвертора синхросигнала выполняют элементы D1 и D2. При выработке любым из этих элементов управляющего нулевого сигнала до переключения M-триггера производиться блокировка элементов D5 и D6, чем обеспечивается сохранение ранее занесенной информации в S-триггер.

28. Привести схему и описать функционирование синхронного JK-триггера на базе MS-триггера с инвертором. Для демонстрации функционирования MS-триггера покажите на временной диаграмме изменение состояний входных сигналов MS-триггера, выходов M-триггера и выходов S-триггера. В чем состоит недостаток схемы MS-триггера с инвертором, как этот недостаток устраняется в схеме с запрещающими связями.

MS-триггер RS-типа легко преобразовать в Jk-триггер путем подключения выходов Q и notQ ко входам R и S соответственно. Так как схема MS-триггера фактически работает в двухтактном режиме (по фронту и спаду синхроимпульса), то проблем с многократным переключением триггера из-за обратных связей, подобных рассмотренным выше Jk-триггерам управляемых уровнем синхросигнала, не будет.

Недостатком в схеме с инвертором является возможность возникновения в нем опасных состязаний при больших разбросах времени задержки распространения сигнала лог.элементов. Если в схеме например сумма времени задержки элементов D2 и D4 будет больше времени задержки инвертора, то процесс занесения информации в М-триггер происходит быстрее, чем будут заблокированы элементы D5 и D6 нулевым сигналом, формируемым на выходе инвертора.

Поэтому возникает опасность того, что вновь поступившая информация будет также занесена в S-триггер во время действия синхроимпульса, а не по его окончании.От этого недостатка свободен MS-триггер с запрещающими связями, в котором функцию инвертора синхросигнала выполняют элементы D1 и D2. При выработке любым из этих элементов управляющего нулевого сигнала до переключения M-триггера производиться блокировка элементов D5 и D6, чем обеспечивается сохранение ранее занесенной информации в S-триггер.

29. Приведите схему и опишите функционирование 4-х разрядного накопительного регистра-защелки с асинхронным сбросом, построенного на D-триггерах. Продемонстрируйте это на временной диаграмме.

В триггере с функцией сброса добавляется еще один вход, называемый RESET (сброс). Когда на

RESET подан 0, сбрасываемый триггер ведет себя как обычный D-триггер. Когда на RESET подана 1, такой триггер игнорирует вход D и сбрасывает выход в 0. Триггеры с функцией сброса

полезны, когда мы хотим ускорить установление определенного состояния (т.е. 0) во всех триггерах системы при первом включении. Такие триггеры могут сбрасываться как синхронно, так

и асинхронно. Синхронно сбрасываемые триггеры сбрасываются только по фронту сигнала CLK.

Асинхронно сбрасываемые триггеры сбрасываются сразу же при поступлении логической единицы на вход RESET, вне зависимости от тактового сигнала.

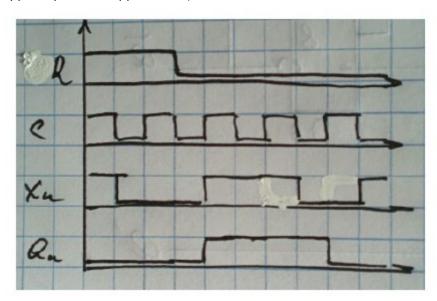

30. Приведите схему, опишите функционирование и нарисуйте временную диаграмму сигналов для двоичного 3-х разрядного счетчика с последовательным переносом и непосредственными связями между разрядами, построенного на синхронных D-триггерах.

Асинхронные счётчики с непосредственными связями: Сигналы синхронизации триггеров старших разрядов снимаются непосредственно с выходов триггеров младших разрядов.

Рис. 3.35. Синхронный последовательный суммирующий счетчик на ЈК -

Импульсы тактового генератора поступают на вход первого каскада деления. Выход первого каскада подключен ко входу второго и т. д. Такую цепочку D-триггеров можно представить и как параллельный регистр с выходам Q0...Q3. Предположим, что в начальный момент все триггера установлены в нулевое состояние. Это значит, что на выходах Q0-Q3 будет присутствовать двоичное число 00002. После поступления на вход схемы первого импульса первый триггер перейдет в единичное состояние. При этом на выходах Q0-Q3 установится 00012. Следующий входной импульс переведет триггер D0 в нулевое состояние. Однако спад выходного импульса этого триггера переведет триггер D1 в единичное состояние. В результате на выходах Q0-Q3 установится число 00102. Далее сигналы на выходах Q0-Q3 будут принимать следующие значения:

00112, 01002, 01012 и так далее, пока не примет значение 11112.

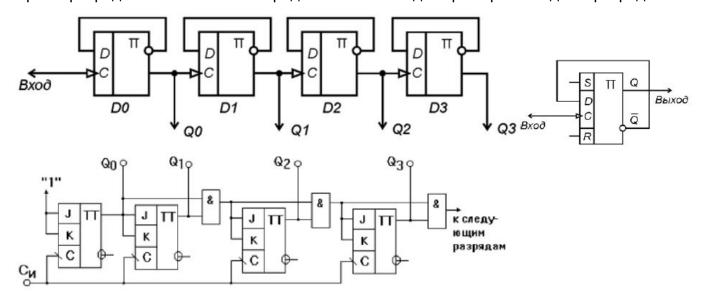

31. Приведите схему, опишите функционирование и нарисуйте временную диаграмму сигналов для двоичного 3-х разрядного счетчика со сквозным переносом между разрядами, построенного на синхронных Т-триггерах.

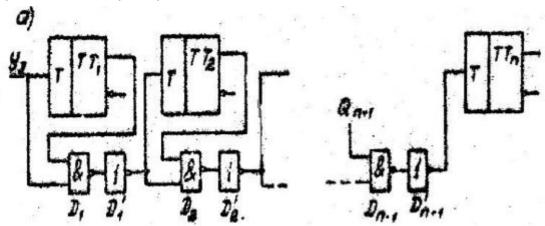

[А ВОТ ЭТО ВООБЩЕ НЕ ПОНЯТНО ЧТО, ИЗ СТАРОГО ДОКУМЕНТА, НО ТУТ ВРОДЕ ВООБЩЕ НЕ СКВОЗНОЙ, хз, но может и сквозной, тут зато хотя бы Т-триггеры] Сквозной перенос – сигнал переноса в старший разряд формируется одновременно (параллельно)

с переключением триггера.

(на схеме - N-разрядный счётчик; в задании - 3-разрядный, т.е. надо просто соединить тут разрыв)

В счетчике со сквозным переносом управляющий сигнал у3 подается одновременно на счетный вход первого триггера и ЛЭ D1, на другой вход которого поступает сигнал с выхода Q1. Этот ЛЭ совместно с инвертором D1 осуществляет операцию совпадения, и если Q1=1, то сигнал на входе TT2 устанавливается до переключения триггера TT1. В свою очередь выход ЛЭ D1 1 связан со входом ЛЭ D2, другой вход которого подключен к выходу Q2 триггера второго разряда и т.д.

В этих счетчиках каждый последующий триггер (i+1) –го разряда запускается от информационных выходов  $(\mathcal{Q}_i,\overline{\mathcal{Q}}_i)$  предыдущего триггера i –го разряда, а счетный сигнал поступает на вход триггера первого разряда.

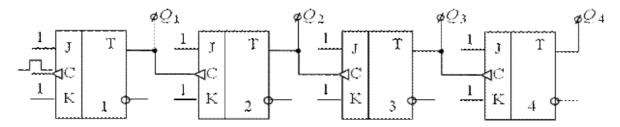

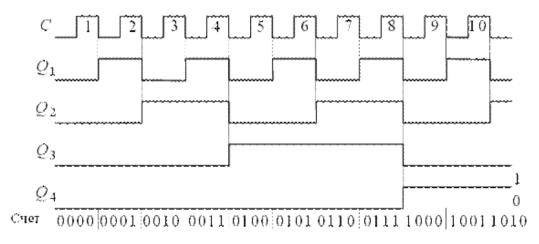

Каждый JK – триггер работает в режиме переключения  $\,(\,J=1,\,K=1\,)\,$  . Пусть в начальный момент состояние выходов счетчика соответствует двоичному числу 0000. При поступлении тактового импульса 1 на синхронизирующий вход (  $^{

m C}$  ) триггера младшего разряда Т1 этот триггер переключается (при прохождении среза импульса). На выходе счетчика появится двоичное число 0001. Тактовый импульс 2 возвращает триггер Т1 в исходное состояние (  $\mathcal{Q}_1 = 0$  ), что в свою очередь приводит к переключению триггера T2 в состояние 1 (  $\mathcal{Q}_2 = 1$ ). На выходе счетчика появится число 0010. Счет продолжается – срез сигнала на выходе каждого триггера запускает следующий триггер. Изменение состояний триггеров происходит последовательно («насквозь»), распространяясь по цепочке. Как видно из временной диаграммы (рис. 1, б), триггер Т2 переключается в два раза реже триггера Т1. Вообще каждый более старший разряд «переключается» в два раза реже предыдущего. следовательно, счетчик можно использовать в качестве делителя частоты. Счетчик, функциональная схема которого показана на рис. 4.1, а, можно назвать не только счетчиком со сквозным переносом, но и счетчиком по модулю 16, 4-разрядным суммирующим счетчиком или асинхронным счетчиком. Определение «асинхронный» говорит о том, что запуск триггеров в счетчике осуществляется не в одно и то же время. Название «счетчик по модулю 16» отражает число различных состояний, «проходимых» счетчиком за один полный цикл счета. Определение «4-разрядный суммирующий» указывает число двоичных разрядов на выходе счетчика, каждое последующее состояние которого (в пределах цикла счета) больше предыдущего.

Недостаток асинхронного счетчика заключается в том, что он имеет зависимость длительности переходного процесса от его разрядности, такая задержка может привести к искажению информации в счетчике.

а – составленный их четырех ЈК – триггеров:

б – его временные диаграммы

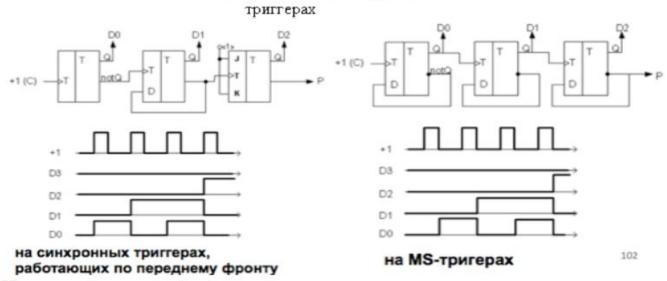

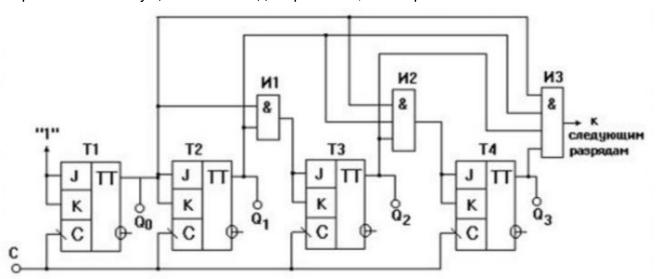

32. Приведите схему, опишите функционирование и нарисуйте временную диаграмму сигналов для двоичного 3-х разрядного синхронного счетчика с параллельным переносом между разрядами, построенного на синхронных ЈК-триггерах.

Параллельный перенос – сигналы переноса в старшие разряды всех триггеров формируются непосредственно от счётного входа всего счётчика.

Стоит вспомнить, что при подаче на входы J=K=1 состояние выходов инвертируется, если J=K=0, то останется прежним. За счет последовательного формирования управляющих уровней, на входы "J" и "K" счетных триггеров, быстродействие последовательных счетчиков несколько уменьшается. От этого недостатка лишены параллельные синхронные счетчики, в которых формирование управляющих уровней и их подача на соответствующие входы триггеров счетчика осуществляется одновременно, т.е. параллельно.

33. Приведите схему, опишите функционирование и нарисуйте временную диаграмму сигналов для двоичного 3-х разрядного счетчика с параллельным переносом между разрядами, с коэффициентом пересчета K=7, построенного на синхронных JK-триггерах.

(Коэффициент пересчёта = до скольки он считает не включительно, т.е. K = 7 -> по модулю 7)

(кроме этого, Q1, Q2 и Q3 все ещё и должны идти на выход на схеме)

(временную диаграмму рисовать лень, но это тупо счётчик, т.е. при каждом такте общее число увеличивается на 1, а когда доходит до 7 - сразу сбрасывается в 0).

34. Нарисуйте схему ПЗУ с диодными элементами. Поясните, как в ячейку памяти записать «1» и «0» и опишите по схеме функционирование памяти в режиме чтения?

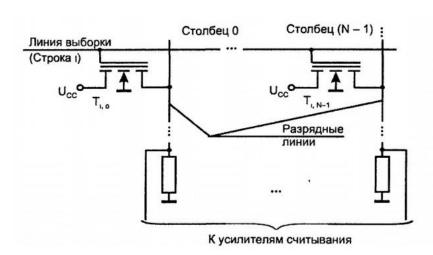

Диоды — это самые простые полупроводниковые приборы, состоящие из одного p - n перехода, задача которых проводить ток в одном направление и не пропускать ток в обратном.

Здесь горизонтальные линии – адресные, а вертикальные – это линии данных, с них в данном случае снимаются 8-разрядные двоичные числа. ЗАПИСЬ: в матрице с диодными элементами в узлах, символизирующих логическую единицу изготавливается полноценный диод, а в узлах, символизирующих логический нуль, присутствует неработоспособный диод. Т.е. для записи 1 ставится полноценный диод, а для записи 0 диод на плате вныжигается и становится неработоспособным.

ЧТЕНИЕ: на вход адреса подаётся значение (A1, A2, A3). Из матрицы выбирается строка, соответствующая поданному значению (напр. если 000, то первый столбец). Все 8 значений столбца подаются на выходы D1..D8.

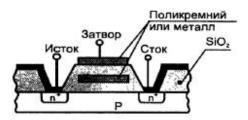

35. Нарисуйте схему масочного ПЗУ с транзисторными элементами. Поясните, как в ячейку памяти записать «1» и «0» и опишите по схеме функционирование памяти в режиме чтения?

Масочные ПЗУ с МОП-транзисторными элементами

Для хранения «0» у транзистора увеличивается толщина подзатворного окисла и поэтому сигнал выборки строки (Ш1) не может открыть этот транзистор и подать через него «1» (напряжение Ucc) на выход.

Рис.1. Фрагмент матрицы с МОП-транзисторами

ЗАПИСЬ: для матриц с МОП-транзисторами при изготовлении транзисторов, символизирующих логический нуль, увеличивают толщину подзатворного слоя. В таких транзисторах рабочее напряжение ЗУ не в состоянии открыть транзистор, что равноценно его отсутствию.

ЧТЕНИЕ: на затвор транзистора подаётся 0 или 1. Если транзистор не рабочий, всегда будет 0. Если транзистор рабочий, то будет 0 при 0 и 1 при 1 (либо наоборот, в зависимости от типа транзистора).

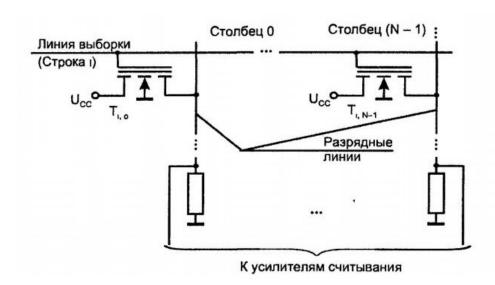

36. Что такое репрограмируемое ПЗУ (РППЗУ)? Покажите конструкцию ЛИЗМОП-транзистора и схему ячейки РППЗУ на ЛИЗМОП-транзисторе. По этим схемам объясните, как происходит запись и стирание информации (значений лог.«1» и лог.«0») в ячейки памяти данного типа.

Структура и функционирование РППЗУ аналогично масочному ПЗУ на базе МОП-транзисторов, но «неоткрываемость» нужных транзисторов обеспечивается не утолщением подзатворного диэлектрика (окисла), а введением блокирующего отрицательного заряда между затвором и каналом.

Основная отличительная особенность РППЗУ состоит в их способности к многоразовому (от 100 до 10 тыс.) перепрограммированию самим пользователем. Это свойство ЗУ, обеспечивается применением элементов памяти со свойствами управляемых "перемычек", функции которых выполняют транзисторы со структурой МНОП (металл AI — нитрид кремния  $Si_3N_4$  — окисел кремния  $SiO_2$  — полупроводник Si) и <u>транзисторы n-МОП с плавающим затвором (ПЗ) с использованием механизма лавинной инжекции заряда ЛИЗМОП.</u>

Тип с плавающим затвором (ЛИЗМОП — МОП-транзис тор с лавинной инжекцией заряда). Принцип работы аналогичен МНОП, но для накопления-удержания заряда используется дополнительный металлический неподключенный - «плавающий» - затвор в слое подзатворного диэлектрика. Такая структура более технологична при производстве и обладает большей надежностью хранения заряда.

<u>СТИРАНИЕ</u>: стирание обеспечивается «рассасыванием» удерживаемого заряда в транзисторах в результате облучения ультрафиолетовыми или рентгеновскими лучами (РППЗУ-УФ/РГ), или в результате «обратно направленного» лавинного пробоя электрическим напряжением (РППЗУ-ЭС, EEPROM)

<u>ЗАПИСЬ</u>: сначала стирается вся линия, потом [каким-то образом] подаём лавинный заряд высокого напряжения (15-20В) в нужные нам ячейки на этой линии (происходит сохранение напряжения в "ловушке" транзистора).

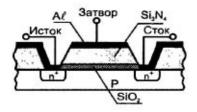

37. Что такое репрограмируемое ПЗУ (РППЗУ)? Покажите конструкцию МНОП-транзистора и схему ячейки РППЗУ на МНОП-транзисторе. По этим схемам объясните, как происходит запись и стирание информации (значений лог.«1» и лог.«0») в ячейки памяти данного типа.

<u>Структура и функционирование</u> РППЗУ аналогично масочному ПЗУ на базе МОП-транзисторов, но «неоткрываемость» нужных транзисторов обеспечивается не утолщением подзатворного диэлектрика (окисла), а введением блокирующего отрицательного заряда между затвором и каналом.

Основная отличительная особенность РППЗУ состоит в их способности к многоразовому (от 100 до 10 тыс.) перепрограммированию самим пользователем. Это свойство ЗУ, обеспечивается применением элементов памяти со свойствами управляемых "перемычек", функции которых выполняют транзисторы со структурой МНОП (металл AI — нитрид кремния  $Si_3N_4$  — окисел кремния  $SiO_2$  — полупроводник Si и транзисторы n-МОП с плавающим затвором (ПЗ) с использованием механизма лавинной инжекции заряда ЛИЗМОП.

Тип с двуслойным подзатворным диэлектриком (МНОП: металл-нитридокисел-полупроводник). Между нитридом и окислом может образоваться «ловушка», удерживающая отрицательный заряд - электроны . «Загрузка» заряда в «ловушку» осуществляется через тонкий слой окисла (менее 5 нм) в результате лавинного пробоя при подаче высокого (15-25В) напряжения программирования

<u>СТИРАНИЕ</u>: стирание обеспечивается «рассасыванием» удерживаемого заряда в транзисторах в результате облучения ультрафиолетовыми или рентгеновскими лучами (РППЗУ-УФ/РГ), или в результате «обратно направленного» лавинного пробоя электрическим напряжением (РППЗУ-ЭС, EEPROM)

<u>ЗАПИСЬ</u>: сначала стирается вся линия, потом [каким-то образом] подаём лавинный заряд высокого напряжения (15-20В) в нужные нам ячейки на этой линии (происходит сохранение напряжения в "ловушке" транзистора).